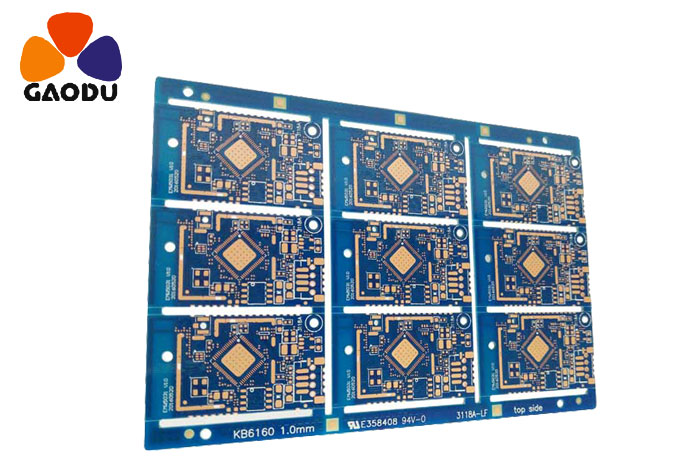

為客戶提供最專業的PCB行業服務

- 服務熱線:13824363925

行業資訊

行業資訊

0

2020-09-29 18:02:02

2020-09-29 18:02:02

1.降低核心電壓也會降低噪聲容限;

2.串擾是電磁場耦合造成的;

3.串擾會隨距離的平方迅速減小,其影響程度與噪聲源的信號電壓及其鄰近度有關。

4.同步總線具有很強的抗串擾能力,它只會在時鐘開啟的瞬間影響很短的窗口范圍;

5.如果電源電壓從3.3V降到1.5V,允許的噪聲容限會降低一半以上;

6.差分技術不存在單端技術的噪聲容限問題,因為共模抑制;

7.受影響線路上的總串擾是附近多個串擾源的總和;

8.帶狀線結構中沒有正向串擾,串擾的幅度會顯著降低;

9.模擬應該將所有信號的最大串擾設置為150mV;除非頻率很高,否則同步總線同組信號的串擾可以忽略不計;

10.正向和反向串擾可以通過將干擾源與受影響的布線分開或者通過減小平面上方/下方的電介質厚度來減小。

雙面板免費加費,四層板加急打樣,厚銅電路板打樣