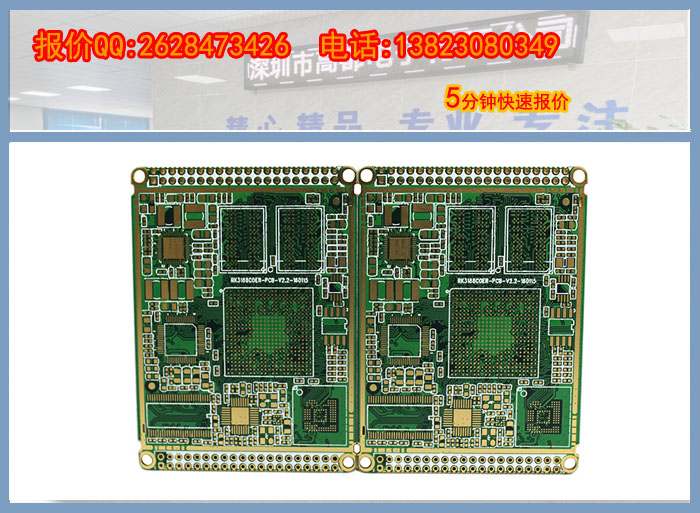

。實踐證明,即使電路原理圖設計正確,印刷電路板設計不當,也會對電子設備的可靠性產生不利影響。例如,如果印刷電路板的兩條細平行線靠得很近,就會形成信號波形的延遲,并在傳輸線的終端形成反射噪聲。因此,建議接地是設計印刷電路板時控制干擾的重要方法。

如果正確使用接地和屏蔽,大多數干擾問題都可以解決。電子設備中的地線結構一般是系統接地、機箱接地(屏蔽接地)、數字接地(邏輯接地)和模擬接地等。地線:的設計應注意以下幾點

1.正確選擇單點接地和多點接地。在低頻電路中,信號的工作頻率小于1兆赫茲,其接線和器件間的電感影響很小,而接地電路形成的環流對干擾影響很大,因此應采用一點接地。當信號工作頻率大于10兆赫時,地線阻抗變得很大。此時,應盡可能降低地線阻抗,并采用最近的多點接地。當工作頻率為1 ~ 10兆赫時,如果采用單點接地,地線長度不應超過波長的1/20,否則應采用多點接地。

2.將數字電路與模擬電路分開。電路板上既有高速邏輯電路,又有線性電路,應使它們盡量分開,而兩者的地線不要相混,分別與電源端地線相連。要盡量加大線性電路的接地面積。

3.試加粗接地線如果接地線很薄,接地電位會隨著電流的變化而變化,這將使電子設備的定時信號電平不穩定,降低抗噪聲性能。因此,接地線應該盡可能厚,以便它可以通過三個印刷電路板的允許電流。如果可能的話,接地線的寬度應該大于3毫米。

4.當接地線被設計成一個閉環電路,而印刷電路板僅由數字電路組成時,將接地線作為一個閉環電路可以明顯提高抗噪聲能力。原因是印刷電路板上有許多集成電路元件,特別是當有消耗大量功率的元件時,由于接地線,厚度的限制,在接地結上會有很大的電位差,這將導致抗噪聲能力下降。如果接地結構處于回路中,電位差將減小,電子設備的抗噪聲能力將提高。實踐證明,即使電路原理圖設計正確,印刷電路板設計不當,也會對電子設備的可靠性產生不利影響。例如,如果印刷電路板的兩條細平行線靠得很近,就會形成信號波形的延遲,并在傳輸線的終端形成反射噪聲。因此,建議接地是設計印刷電路板時控制干擾的重要方法。

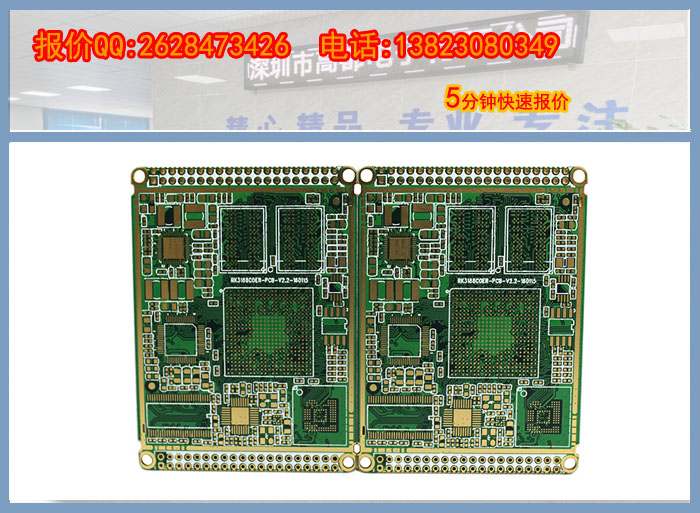

如果正確使用接地和屏蔽,大多數干擾問題都可以解決。電子設備中的地線結構一般是系統接地、機箱接地(屏蔽接地)、數字接地(邏輯接地)和模擬接地等。地線:的設計應注意以下幾點

1.正確選擇單點接地和多點接地。在低頻電路中,信號的工作頻率小于1兆赫茲,其接線和器件間的電感影響很小,而接地電路形成的環流對干擾影響很大,因此應采用一點接地。當信號工作頻率大于10兆赫時,地線阻抗變得很大。此時,應盡可能降低地線阻抗,并采用最近的多點接地。當工作頻率為1 ~ 10兆赫時,如果采用單點接地,地線長度不應超過波長的1/20,否則應采用多點接地。

2.將數字電路與模擬電路分開。電路板上既有高速邏輯電路,也有線性電路,所以應盡量分開,兩者的地線不要混在一起,應分別與電源端的地線相連。盡量擴大線性電路的接地面積。

3.試加粗接地線如果接地線很薄,接地電位會隨著電流的變化而變化,這將使電子設備的定時信號電平不穩定,降低抗噪聲性能。因此,接地線應該盡可能厚,以便它可以通過三個印刷電路板的允許電流。如果可能的話,接地線的寬度應該大于3毫米。

4.當接地線被設計成一個閉環電路,而印刷電路板僅由數字電路組成時,將接地線作為一個閉環電路可以明顯提高抗噪聲能力。原因是印刷電路板上有很多集成電路元件,特別是當有功耗大的元件時,由于接地線,厚度的限制,接地結上會產生很大的電位差,導致抗噪聲能力下降。如果接地結構為回路,電位差將減小,電子設備的抗噪聲能力將提高

行業資訊

行業資訊

2020-07-14 18:12:39

2020-07-14 18:12:39

。實踐證明,即使電路原理圖設計正確,印刷電路板設計不當,也會對電子設備的可靠性產生不利影響。例如,如果印刷電路板的兩條細平行線靠得很近,就會形成信號波形的延遲,并在傳輸線的終端形成反射噪聲。因此,建議接地是設計印刷電路板時控制干擾的重要方法。

。實踐證明,即使電路原理圖設計正確,印刷電路板設計不當,也會對電子設備的可靠性產生不利影響。例如,如果印刷電路板的兩條細平行線靠得很近,就會形成信號波形的延遲,并在傳輸線的終端形成反射噪聲。因此,建議接地是設計印刷電路板時控制干擾的重要方法。