為客戶提供最專業的PCB行業服務

- 服務熱線:13824363925

行業資訊

行業資訊

0

2020-08-06 14:37:02

2020-08-06 14:37:02

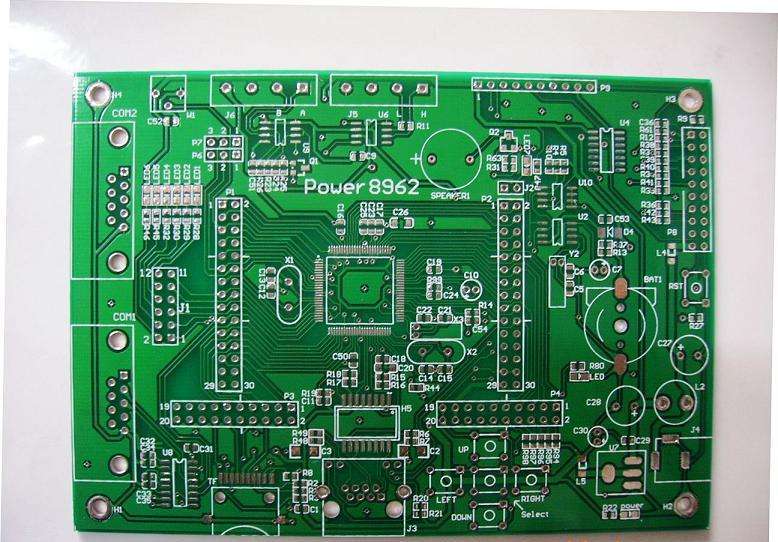

1.組件配置

(1)不要有太長的平行信號線;

(2)確保印刷電路板的時鐘發生器、晶體振蕩器和中央處理器的時鐘輸入端盡可能靠近,遠離其他低頻設備;

(3)應圍繞核心設備配置組件,以最小化引線;長度

(4)分發印刷電路板;

(5)考慮pcb在機箱中的位置和方向;

(6)縮短高頻分量之間的引線。

2.去耦電容器的配置

(1)每10個集成電路應增加一個充放電電容(10uf );

(2)低頻采用引線電容,高頻采用片式電容;

(3)每個集成芯片應配備一個0.1uf的陶瓷電容;

(4)抗噪聲能力弱、關斷時功率變化大的設備應增加高頻去耦電容;

(5)電容器之間不要共用過孔;

(6)去耦引線電容器不應過長。

3.降低噪音和電磁干擾的原理

(1)盡量使用45 折線而不是90 折線(盡量減少高頻信號的外部發射和耦合);

(2)使用串聯電阻降低電路信號邊沿的跳變率;

(3)應時晶體振蕩器的外殼應接地;

(4)不要掛起空閑電路;

(5)當時鐘垂直于輸入輸出線時,干擾很小;

(6)盡量使晝夜電動勢趨于零;

(7)輸入輸出驅動電路盡可能靠近印刷電路板的邊緣;

(8)不要與任何信號形成回路;

(9)對于高頻電路板,電容的分布電感不可忽略,電感的分布電容也不可忽略;

(10)通常,功率線和交流線在盡可能不同于信號線的板上。

雙面板免費加費,四層板加急打樣,厚銅電路板打樣