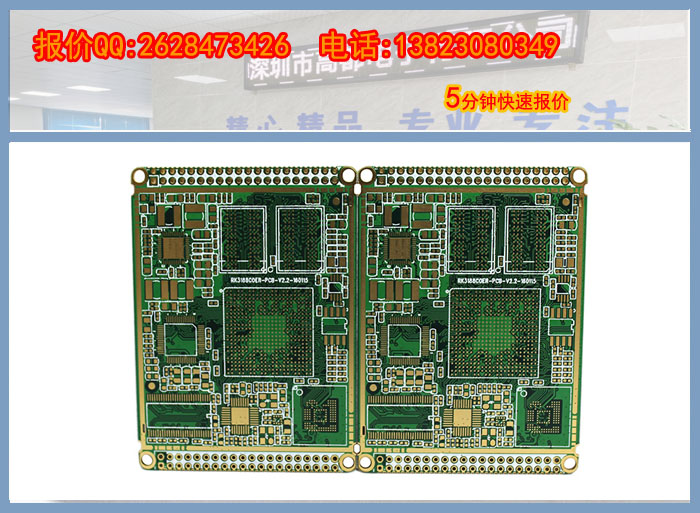

為客戶提供最專業的PCB行業服務

- 服務熱線:13824363925

行業資訊

行業資訊

0

2020-08-06 14:39:57

2020-08-06 14:39:57

地線的設計原則是:

(1)數字地與模擬地分開。如果電路板上既有邏輯電路又有線性電路,它們應盡可能分開。低頻電路的接地應盡可能單點并聯接地。當實際接線有困難時,可以串聯,然后并聯接地。高頻電路應采用多點串聯接地,地線應短而租,高頻元件周圍應盡可能采用網格狀大面積接地箔。

(2)連接地線應盡可能大膽。如果地線與很細的線連接,接地電位會隨著電流的變化而變化,這降低了抗噪聲性能。因此,地線應該加厚,以便它可以通過印刷電路板上允許電流的三倍。如果可能,連接地線應大于2 ~ 3毫米

(3)與地線連接形成一個閉環。對于僅由數字電路組成的印刷電路板,將數字電路的接地電路排列成一組回路可以提高抗噪聲能力。

二、去耦電容配置

印刷電路板設計的常見做法之一是在印刷電路板的所有關鍵部分配置適當的去耦電容。

去耦電容的一般配置原則是:

(1)在電源輸入端跨接一個10~100uf的電解電容。如果可能,最好連接到100uF以上。

(2)原則上,每個集成電路芯片應配備一個0.01pF的陶瓷芯片電容,在印刷電路板間隙不足的情況下,每4-8個芯片可配備一個1-10 pf的電容。

(3)對于抗噪聲能力弱、關機時電源變化大的器件,如內存和只讀存儲器器件,應在芯片電源線和地線之間直接連接去耦電容

(4)電容器的引線不應太長,特別是高頻旁路電容器不應有引線

雙面板免費加費,四層板加急打樣,厚銅電路板打樣